平台介绍

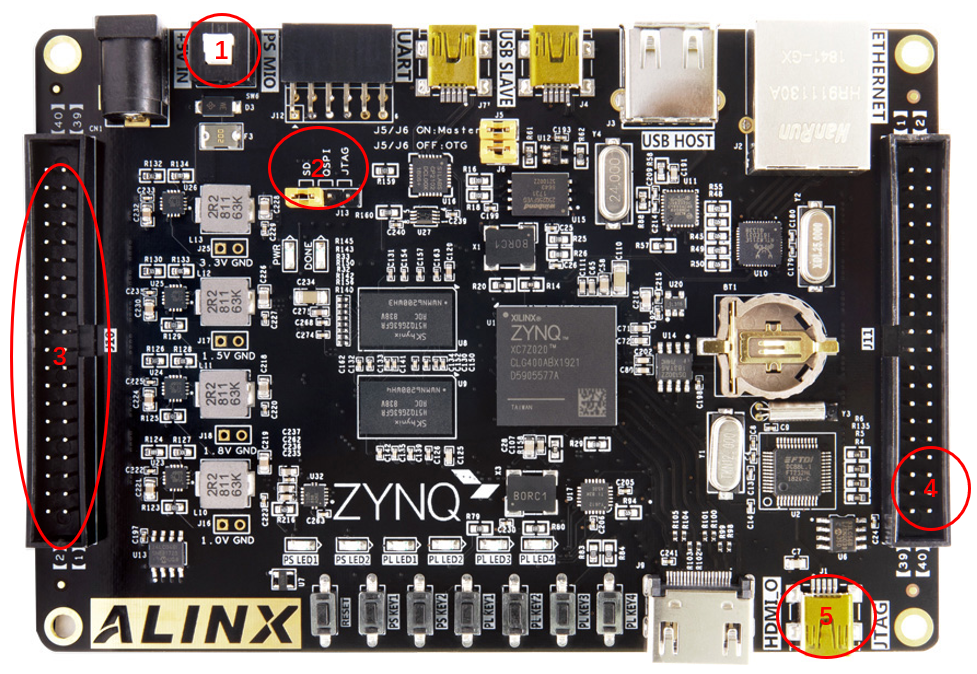

本次实验使用的开发板用到了Xilinx Zynq7000系列的芯片,型号为 XC7Z020-2CLG400I。此外,还有一块拓展板,主要包含LED和矩阵键盘模块。开发板如下图所示:

在接下来的实验中,我们仅用到开发板的PL部分。

电源开关

图中红框1的部分是电源键,按下之后开启。电源键左边部分是电源接口。

GPIO接口

图中红框3部分,是外围拓展电路的接口。在接下来的实验中, 我们将矩阵键盘模块插入到该位置。

JTAG

图中红框5部分,是一个JTAG下载器。我们通过该接口将比特流从电脑传输到开发板上。

DAP调试器

图中红框4的部分,我们连接了一个DAP调试器。在搭建基于 Cortex-M0 的 SoC 时,调试系统是必不可少的。在接下来的实验中,我们外接一个DAP调试器。调试器部分的端口约束了一个时钟信号和一个双向的数据信号。具体情况可以在 .xdc 的约束文件中看到。 在搭建基于 Cortex-M0 的 SoC 时,调试系统是必不可少的。

为什么会有两个接口?

上面的 DAP-LINK 的接口是用来调试 FPGA 中的 SoC 的, 下面的 JTAG 接口是用来下载比特流文件的.

通俗的来说, 当你想要把 Verilog 代码下载到 FPGA 开发板上时, 你应该使用下面的接口; 当你想要使用汇编语言或者 C 语言来控制 FPGA 中实现的 SoC 时, 你应该使用上面的接口. 这部分内容我们将会在LAB2: "点石成金" - 实现你的首个 SoC中涉及.

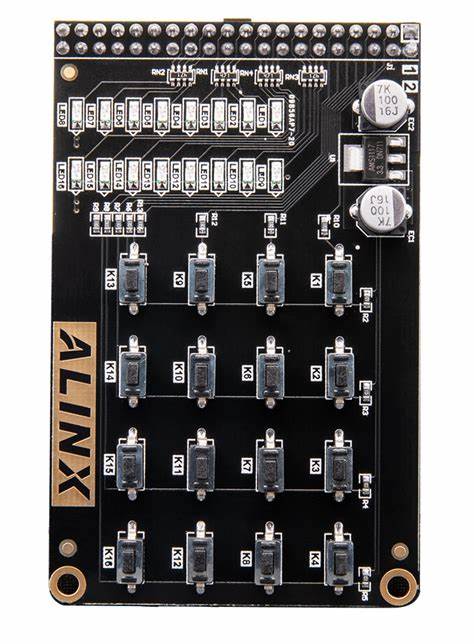

矩阵键盘

接下来的实验中,我们外接了一个矩阵键盘模块。

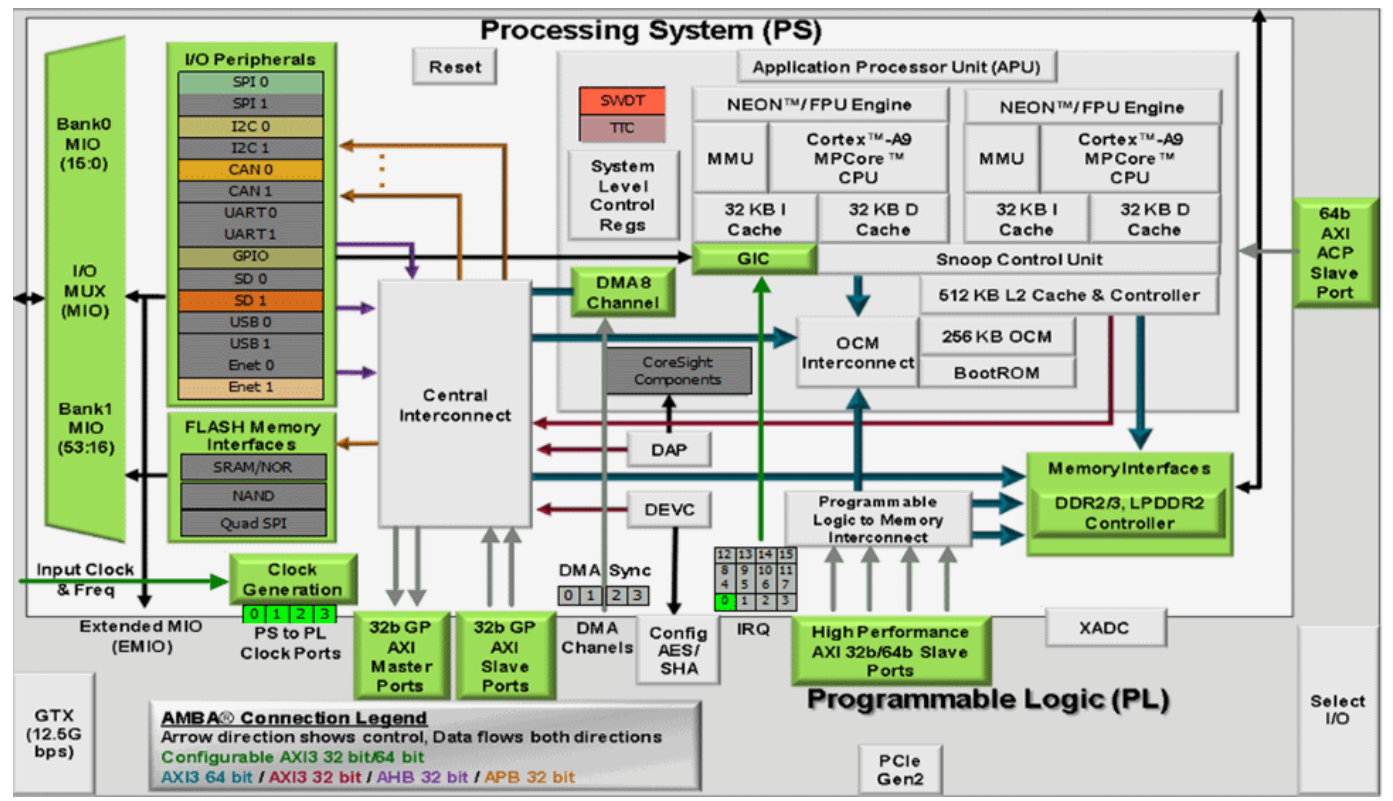

FPGA芯片

对于本实验开发板使用的ZYNQ7000系列芯片,PL逻辑部分主要参数如下:

- 逻辑单元 Logic Cells:85K

- 查找表 LUTs:53,200

- 触发器 flip-flops:106,400

- 乘法器 18x25MACCs:220

- Block RAM:4.9 Mb

- 2个A/D转换器,可以测量片上电压,温度感应和高达17外部差分输入通道,1MBPS

在使用 HDL 语言描述时如果想要利用 FPGA 内部的 Block RAM 进行实现,,需要在 HDL 代码中加入一些声明,这在之后章节会进行详细的介绍。

使用板子时请注意

在使用 FPGA 时, 一定要注意资源的合理利用以及避免出现时序问题. 在复杂系统中, 时序违例是一个很严重的问题, 通常是由于时钟周期小于关键路径(critical path)导致. 但现在的 EDA 工具的时序分析功能已经非常强大, 所以我们在学习时一定要多看工具输出的报告, 养成良好的习惯.