平台介绍

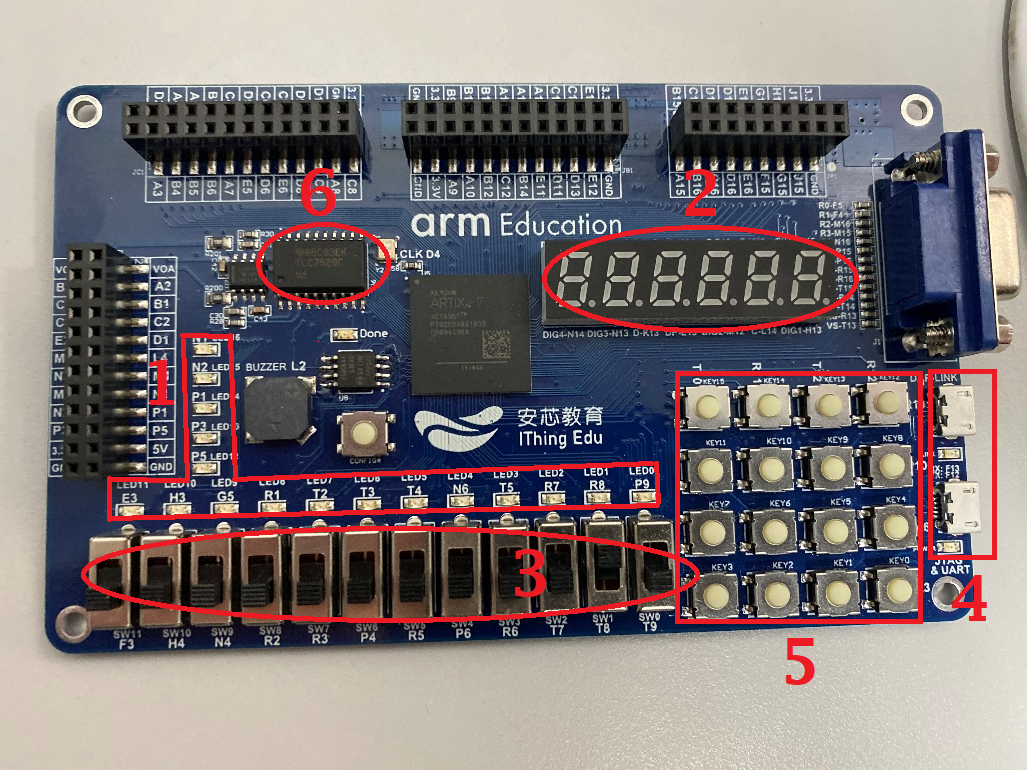

本次实验使用的 FPGA 芯片型号为 Xilinx ARTIX-7 35t, 使用的开发板如下图.

一般来说, 开发板包含基本输入操作类模块、输出显示类模块、蜂鸣器发声模块、时钟模块、I/O 扩展类模块、存储类模块及电源模块. 其中, 基本输入操作类模块主要有拨码开关和矩阵键盘, 用于向系统输入中断信号或操作信号. 输出显示类模块主要用于将实验结果通过 LED 灯或七段数码管表现出来. I/O 扩展类模块主要用于扩展外设, 接收外设输入的信号或向外设输出信号. 本节将对 FPGA 板上的各部分做一个简单的介绍.

LED 灯

LED 灯对应上图中红框 1 的部分. 本次实验使用的开发板提供 17 个直接由 FPGA 引脚驱动的 LED 灯 LED0 - LED16, 当 FPGA 输出高电平时, LED 灯点亮.

数码管

数码管对应上图中红圈 2 的部分. 开发板上配有6个七段数码管 DIG1-DIG6(当正放 FPGA 开发板时, 从左至右为 1-6), 每个数码管都由一个专用片选信号(DIG1- DIG6)控制. 七段数码管的每个引脚(共阴模式)均连接到 FPGA 芯片上, 当 FPGA 输出高电压时, 对应的字码段点亮, 反之则熄灭. 七段数码管的片选信号也直接与 FPGA 引脚相连, 当 FPGA 输出低电压时, 对应的数码管选中, 反之则不选中.

拨码开关

拨码开关对应上图中红圈 3 的部分. 开发板上有 12 个拨动开关 SW11-SW0, 当拨动开关处在 DOWN 位置(靠近开发板边缘)时向 FPGA 相应引脚输入低电平, 当拨动开关在 UP 位置时向 FPGA 相应引脚输入高电平.

调试模块

调试模块对应上图中红圈 4 的部分. 在搭建基于 Cortex-M0 的 SoC 时, 调试系统是必不可少的. 为了方便使用, FPGA 开发板在设计之初便将调试电路封装在板上, 预留出来一个 JTAG 口用于和 PC 机通信, 这样做不仅简化了对调试器内部原理的理解需求, 而且方便了连线. 调试器部分的端口需要约束的有一个时钟信号和一个双向的数据信号. 调试时需要注意.

为什么会有两个接口?

上面的 DAP-LINK 的接口是用来调试 FPGA 中的 SoC 的, 下面的 JTAG 接口是用来下载比特流文件的.

通俗的来说, 当你想要把 Verilog 代码下载到 FPGA 开发板上时, 你应该使用下面的接口; 当你想要使用汇编语言或者 C 语言来控制 FPGA 中实现的 SoC 时, 你应该使用上面的接口. 这部分内容我们将会在LAB2: "点石成金" - 实现你的首个 SoC中涉及.

矩阵键盘

矩阵键盘对应上图中红框 5 的部分. FPGA 板带有一个 4 x 4 的矩阵键盘, 可以用于一些外界的控制交互. 左侧的 KEY1 - KEY8 信号分别代表横竖的4个端口, 分别与 FPGA 上的 4 个输出端口连接. 矩阵键盘的工作原理可以举个例子说明, 如果将 KEY1 设置为低电平, KEY2 - KEY4 设置为高电平, 则按下 KEY15 按键后, KEY5 端口输出低电平, 松开 KEY15 按键后, KEY5 端口输出高电平. 唯一需要注意的是, 按下按键时信号存在抖动, 所以需要设计按键消抖模块以免按键抖动带来未预期的系统错误.

数模转换器(DAC)芯片

数模转换器对应上图中红圈 6 的部分. 为了与外界更好地进行通信, 通常需要 DAC 芯片进行数字信号到模拟信号的转换. 本书使用的 FPGA 开发板带有 TLC7528C 型号的 DAC 芯片. DAC全称 Digital-to-Analog Converters, 属于一种数据转换器, 在满足一定时序的条件下, 将数字信号转换为模拟信号输出. TLC7528C 是双口, 8 位的 DAC 芯片, 有单独的片上数据锁存器. 数据通过一个公共的 8 位输入端口传输到两个 DAC 数据锁存器中的任何一个. 这些设备的加载时序与随机存取存储器的写入时序相似, 从而可以轻松地与大多数流行的微处理器总线和输出端口连接.

FPGA芯片

Xilinx 7 系列 FPGA 包括 4 种 FPGA 种类, 分别是 Spartan、Artix、Kintex、Virtex. 其中 Spartan-7 是 7 系列中最低端的种类, Artix-7 针对功耗进行了优化, Kintex-7 性价比较高, 而 Virtex-7 拥有最强悍的性能. 虽然现在的综合工具非常强大, 但是在编写 HDL 代码时, 我们仍需要良好的代码风格, 在使用 Artix 系列 FPGA 时, 需要注意以下几点:

CLB 中触发器有一个 set 信号和一个 reset 信号, 不能同时使用 set 和 reset 信号.

触发器资源丰富, 可以考虑使用流水线(pipeline)提高性能.

控制输入在 slice 或 CLB 之间共享. 设计所需的控制信号输入的数量应该最小化. 控制信号输入包括时钟, 时钟使能, 设置/复位和写使能.

6输入 LUT 可以用作 32 位移位寄存器, 以满足复杂系统需求, 也可用作 64 x 1 存储器, 以满足小型存储需求.

专用进位逻辑可有效实现算术功能.

在 Xilinx ARTIX 7 系列 FPGA 中的 Block RAM 可存储多达 36 Kbit 的数据, 并可配置为两个独立的 18 K RAM或一个 36 Kb RAM. 每个 36 Kb Block RAM 可以配置为 64K x 1(与相邻的 36K Block RAM 级联时), 32K x 1、16K x 2、8K x 4、4K x 9、2K x 18、1K x 36 或在简单双端口模式下的 512 x 72. 在简单的双端口模式下, 每个 18 Kb Block RAM 可以配置为 16K x 1、8K x2、4K x 4、2K x 9、1K x 18 或 512 x 36. 在使用 HDL 语言描述时如果想要利用 FPGA 内部的 Block RAM 进行实现, 需要在 HDL 代码中加入一些声明, 这在之后章节会进行详细的介绍.

使用板子时请注意

在使用 FPGA 时, 一定要注意资源的合理利用以及避免出现时序问题. 在复杂系统中, 时序违例是一个很严重的问题, 通常是由于时钟周期小于关键路径(critical path)导致. 但现在的 EDA 工具的时序分析功能已经非常强大, 所以我们在学习时一定要多看工具输出的报告, 养成良好的习惯.