下载比特流到 FPGA

上一小节中, 我们通过仿真验证了 SoC 的功能, 接下来我们将系统实现在 FPGA 上, 进行上板调试.

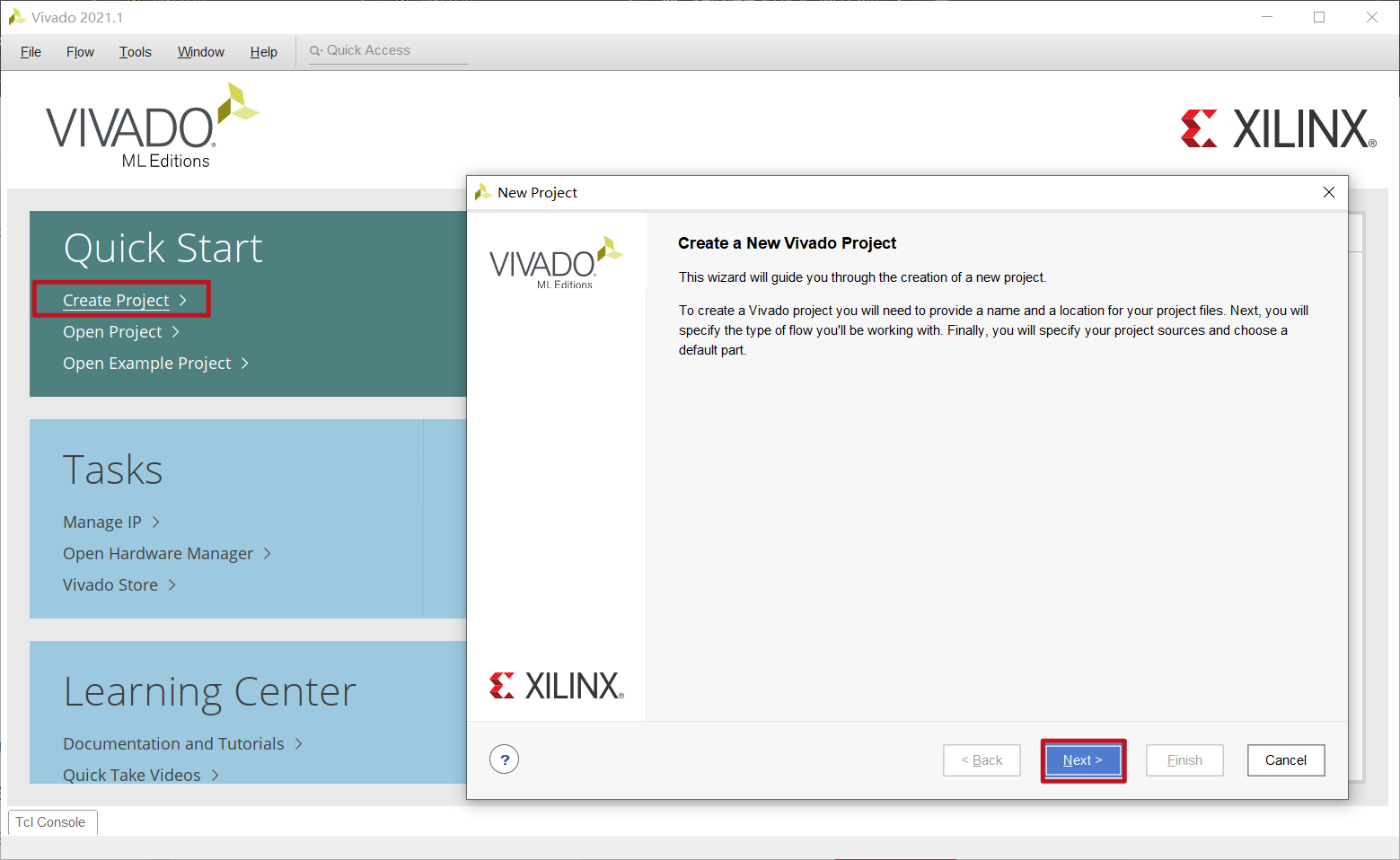

打开 Vivado 软件, 点击 Create Project, 创建一个新的工程.

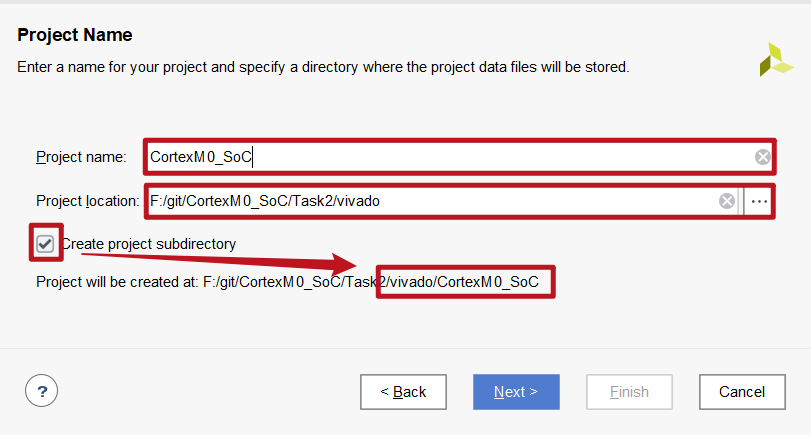

点击 Next, 给工程命名为 "CortexM0_SoC", 工程文建立在 "/Task2/vivado/" 文件夹下. 记得检查一下下方显示的工程路径是否合理.

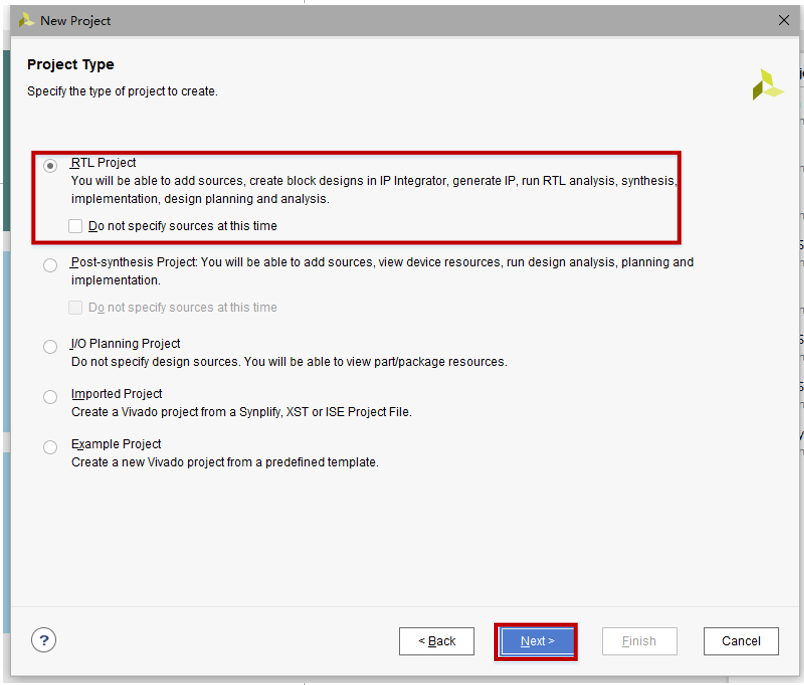

点击 Next, 选择工程类型为 RTL Project.

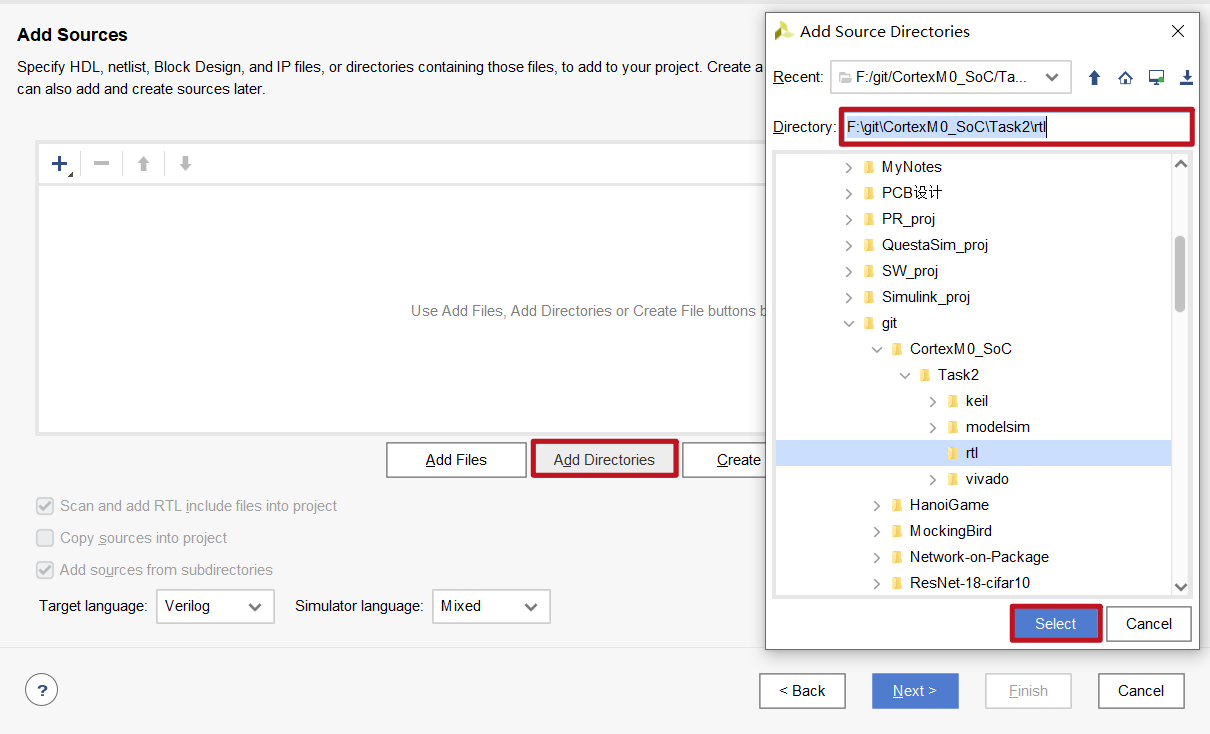

点击 Next, 进入源文件添加界面, 因为我们的设计源文件都在 "/Task2/rtl" 下, 所以这里点击 Add Directory, 直接将 "/Task2/rtl" 目录添加进来.

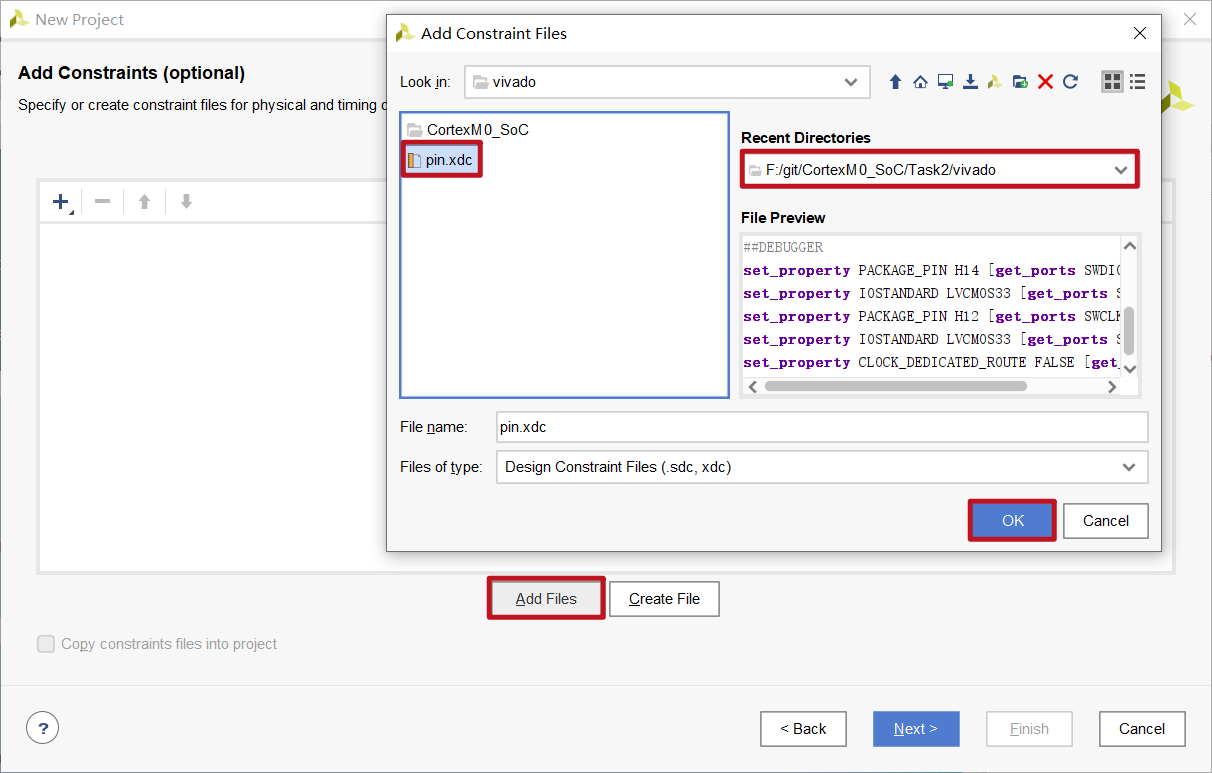

点击 Next, 进入约束文件添加界面, 我们已经在 "/Task2/vivado/" 中为你准备好了约束文件 "pin.xdc", 将这个文件添加进来即可.

什么是约束文件?

- 本实验中的约束文件用于将设计的外部端口连接到 FPGA 的物理引脚上.

- 除了引脚约束之外, 约束文件还可以用于时钟约束, 常用于静态时序分析 (STA).

- 不同的开发工具采用的约束文件格式是不同的, Vivado 中的约束文件以 .xdc 为后缀.

本实验中的约束文件

打开 "/Task2/vivado/pin.xdc":

##clk

set_property PACKAGE_PIN D4 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

##RSTn

set_property PACKAGE_PIN T9 [get_ports RSTn]

set_property IOSTANDARD LVCMOS33 [get_ports RSTn]

##DEBUGGER

set_property PACKAGE_PIN H14 [get_ports SWDIO]

set_property IOSTANDARD LVCMOS33 [get_ports SWDIO]

set_property PACKAGE_PIN H12 [get_ports SWCLK]

set_property IOSTANDARD LVCMOS33 [get_ports SWCLK]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets SWCLK]

上述代码中, clk 管脚约束到 FPGA 开发板上的 50MHZ 时钟; RSTn 管脚约束到 SW0 开关, 开关向上拨时, 连接到电源 VDD 上, 此时 SoC 才可以工作.

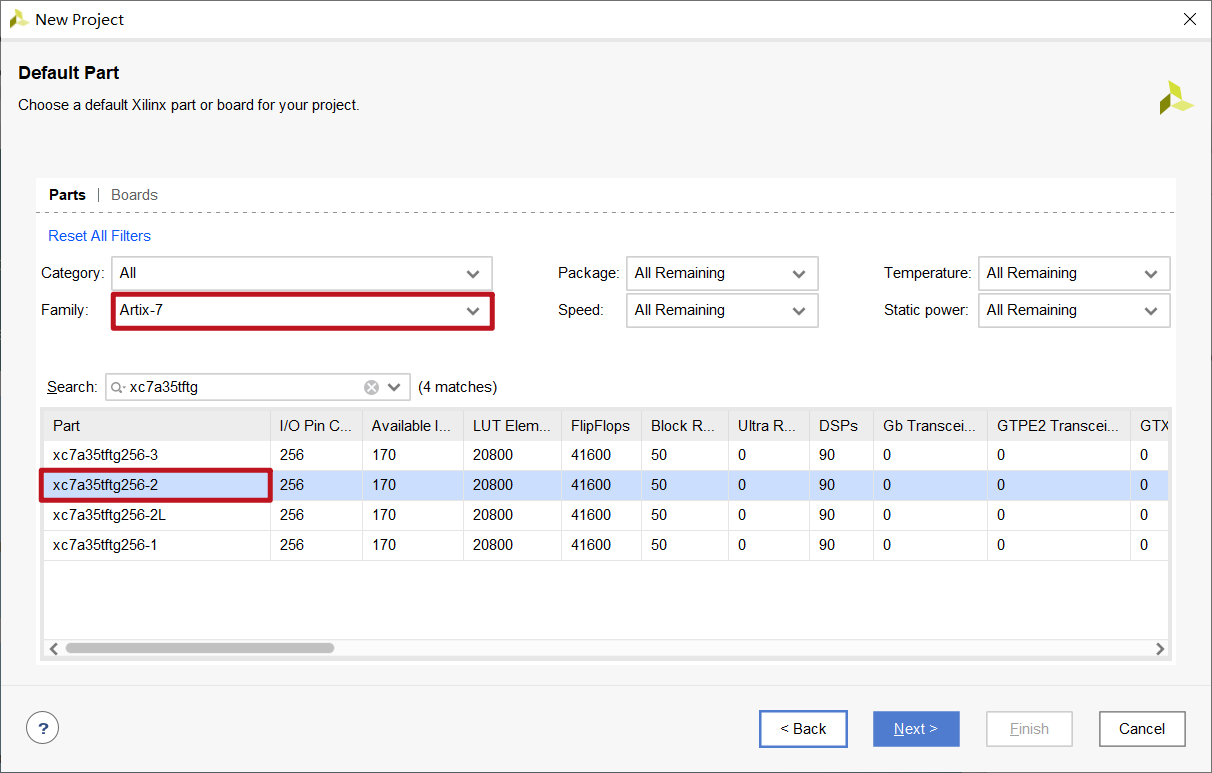

点击 Next, 选择 FPGA 芯片型号, 首先在 Family 栏处选择 Artix-7, 然后在下方列表中选择 xc7a35tftg256-2.

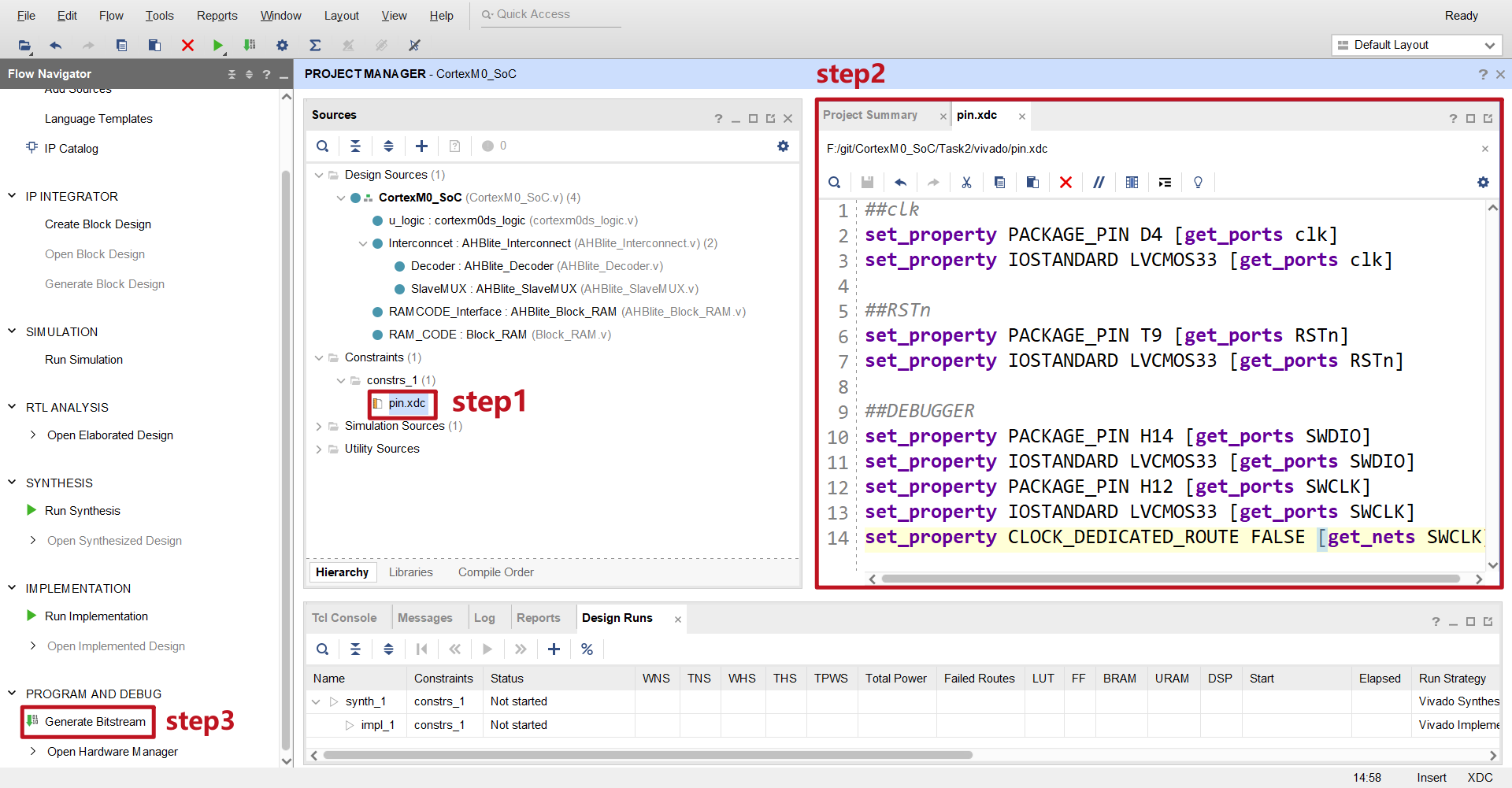

之后一直点击 Next, 直到出现工程创建完成的界面, 点击 Finish, 完成 Vivado 工程的创建. 在进入 Vivado 主界面后, 可以在 Source 窗口的 Hierarchy 标签页中看到我们的设计文件, 仿真文件和约束文件. 若要对某个文件临时进行编辑, 以约束文件为例, 我们可以双击 "pin.xdc", 该文件的内容会被显示到右侧的编辑窗口中.

Hierarchy 和 Libraries

- Hierarchy 标签页是对设计的层次化展示, 便于我们直观理解多个模块之间的调用关系. Vivado 会自动选择设计的顶层文件, 并标上

图标. 你也可以通过右键文件选择 Set as Top 将任意文件设为顶层文件. 注意, RTL 分析, 综合和实现的对象都是顶层文件.

图标. 你也可以通过右键文件选择 Set as Top 将任意文件设为顶层文件. 注意, RTL 分析, 综合和实现的对象都是顶层文件. - Libraries 标签页是对所有文件的平铺罗列, 方便用户添加和删除文件.

然后点击左侧导航栏下方的 Generate Bitstream, 这时 vivado 将会依次执行 RTL 分析 (RTL Analysis), 综合 (Synthesis), 实现 (Implementation) 和 生成比特流文件 (Generate Bitstream) 四个步骤. 最终生成的比特流文件用于 FPGA 的配置.

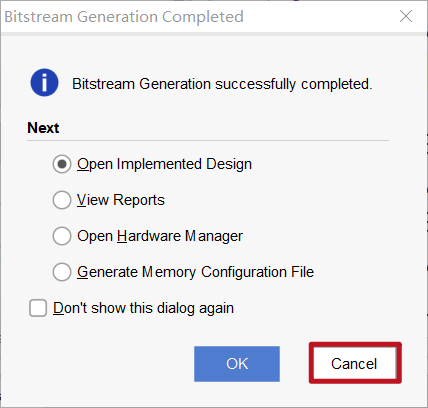

等待 Vivado 运行一段时间后, 可以看到弹出的比特流下载成功提示窗口, 关闭该窗口.

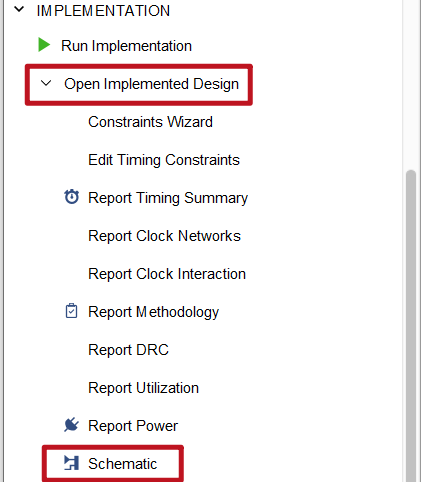

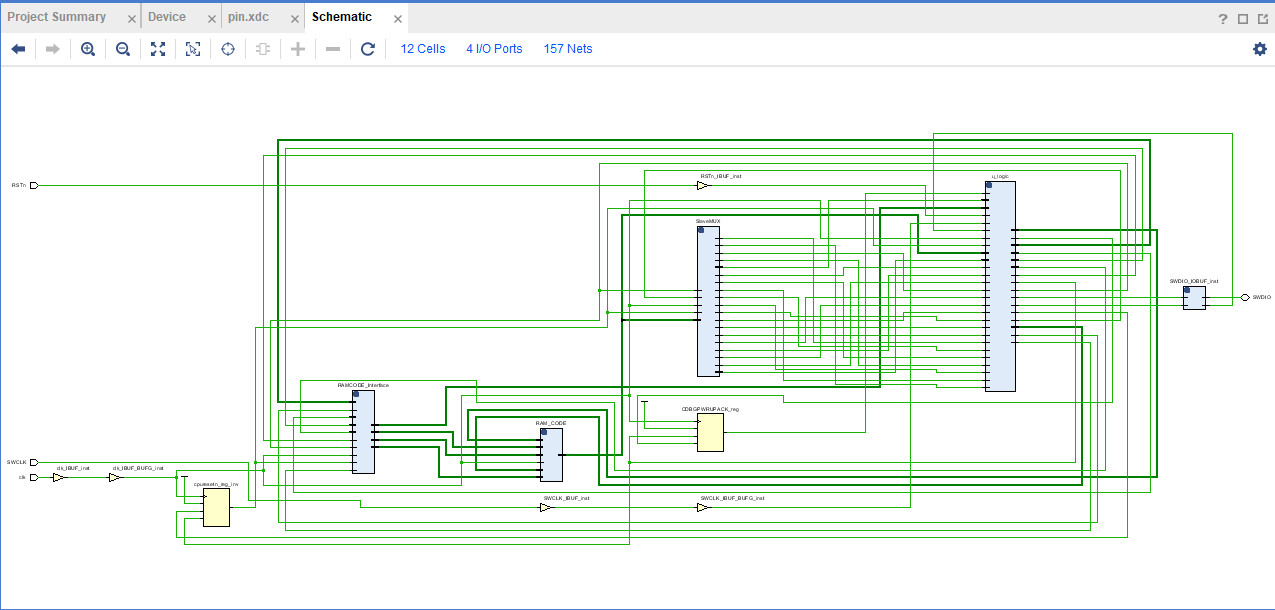

点击左侧导航栏中 Open Implemented Design 下的 Schematic 选项, 可以看到综合和布局布线得到的原理图.

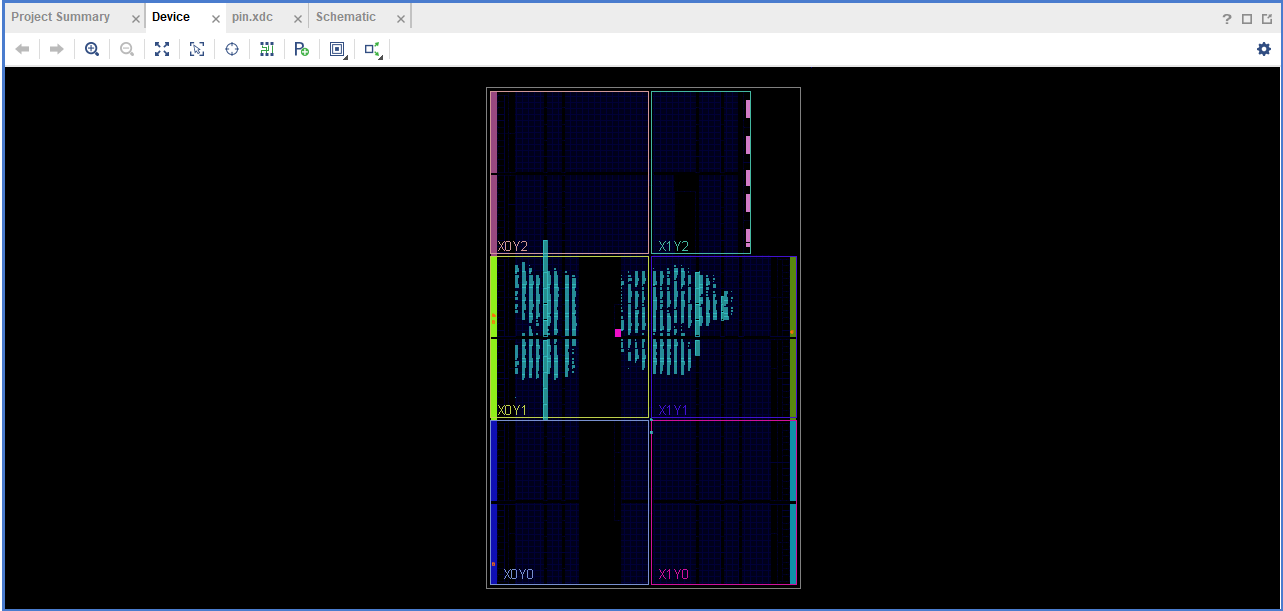

点击 Schematic 标签旁的 Device, 可以看到设计对 FPGA 内部资源的占用情况.

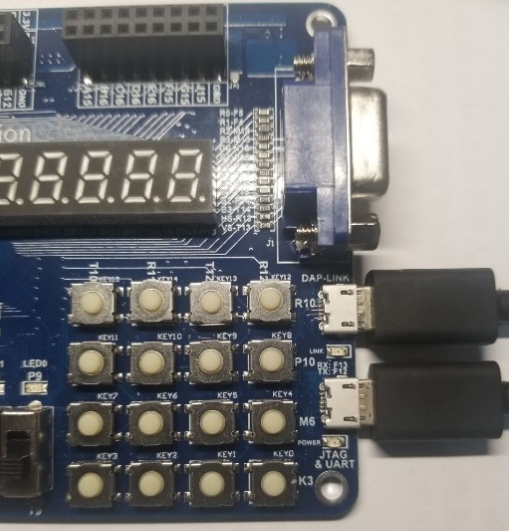

接下来进行板卡的连接. 使用两条数据线将 FPGA 板卡上的两个 Micro-USB 接口与 PC 上的两个 USB 接口连接起来.

为什么是两个接口?

- 标有 JTAG & UART 的接口是 FPGA 的下载配置接口, 用于比特流文件或其他配置文件的下载.

- 标有 DAP-Link 的接口是 CMSIS 调试接口, 用于 FPGA 中实现的 CortexM0 的调试. 该接口与板卡上的 CMSIS-DAP 调试器连接, 该调试器的另一端连接在 FPGA 的引脚上, 这些引脚通过约束文件与 CortexM0 的 SWDIO 和 SWCLK 这两个调试信号连接.

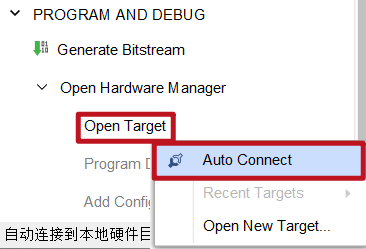

确保连线无误后, 依次点击左侧导航栏中的 Open Target -> Auto Connect, 进行 PC 与 FPGA 的连接.

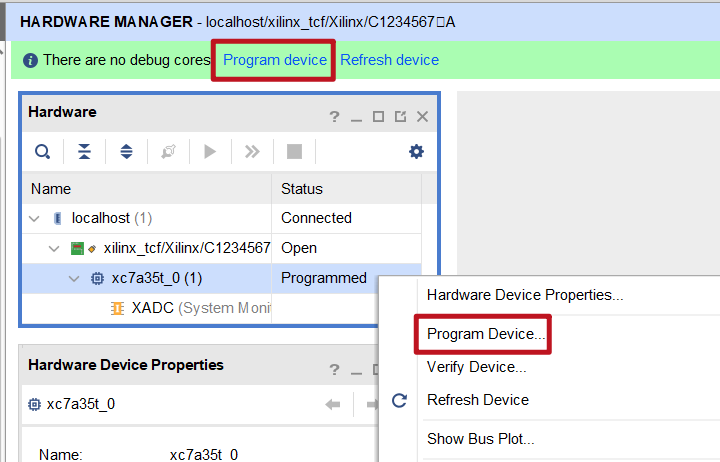

Hardware 窗口中出现了 xc7a35t_0 器件, 这表明我们的 PC 已经连接上了 FPGA 芯片, 这时我们可以点击上方的 Program device, 也可以右键 xc7a35t_0 器件, 然后点击下拉栏中的 Program Device, 进行比特流下载.

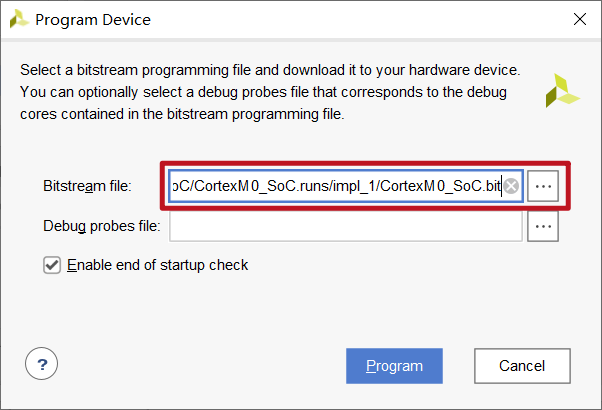

这时会弹出来一个窗口, 让你选择待下载的比特流文件, 这里一般系统会默认指定刚生成的比特流文件路径. 但这里仍要格外注意, 因为当你在多个工程间来回穿梭时, Vivado 可能会突然抽风, 给你默认指定一个其他工程中的比特流文件, 如果你没有注意而将它下载了进去, 那么接下来的调试工作可能会让你心态爆炸.

Vivado 的工程目录结构

为了更好地帮助你找到工程中的文件(如日志文件,比特流文件等), 这里有必要简单介绍一下 Vivado 默认的工程目录结构.

- ProjectName.srcs: 存放源文件

- sources_1: 设计源文件(只针对新建的文件, 如果是用户提前准备好的源文件, 则不用关心其存放路径)

- sim_1: 仿真源文件 (testbench 文件)

- ProjectName.runs: 存放综合实现的中间文件和结果文件

- synth_1: 与整个设计有关的综合 (Synthesis) 文件

- impl_1: 与整个设计有关的实现 (Implementation) 文件, 包括比特流文件和 bin 文件等

- ProjectName.sim: 存放和仿真有关的文件, 最常用的就是日志文件

选择好比特流文件的路径之后, 点击 Program 开始下载比特流, 等待进度条加载完毕, 便可开始下一步的调试工作了.

思考

我们知道, 下载比特流文件是将硬件电路配置到 FPGA 中, 那么我们的软件程序是如何被下载到 FPGA 中的呢?

还记得我们使用 keil 生成的 "code.hex" 文件对 RAM 进行了初始化. 所以在生成比特流文件时, RAM 的初始数据, 即程序的指令代码也就成为了比特流文件的一部分, 被下载到了 FPGA 中.

万物皆可命令行

没错, Vivado 同样采用 TCL 命令, 可以使用命令行和脚本进行操作.

如果你有兴趣就自己去学习尝试吧~