软硬件关系

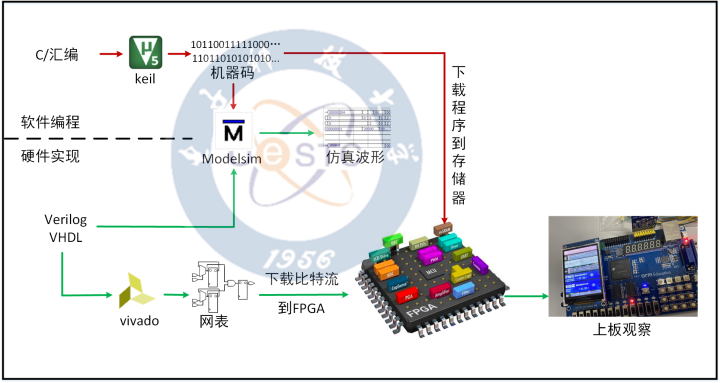

本节和接下来的三节将要介绍本次实验过程中用到的三个软件: Modelsim, Vivado, Keil. 下图是它们的依赖关系.

从上图中可以看出, Vivado 负责将硬件描述语言(Verilog/VHDL)所描述的 SoC 编译、综合、实现, 将 FPGA 内部本身无序的各种逻辑资源(如查找表、触发器、RAM 等)配置成为有序的电路, 实现 SoC 功能. 而 Keil 负责将编写的软件编程语言(C / 汇编)编译成为机器码十六进制文件. 将机器码作为 RAM 的初始化内容, 即可进行仿真, 在 Modelsim 软件中观察 SoC 工作时各个信号的波形. 若将机器码通过工具下载到由 FPGA 实现的 SoC 中, 那么就可以让 SoC 执行编写的程序, 通过开发板观察执行结果.

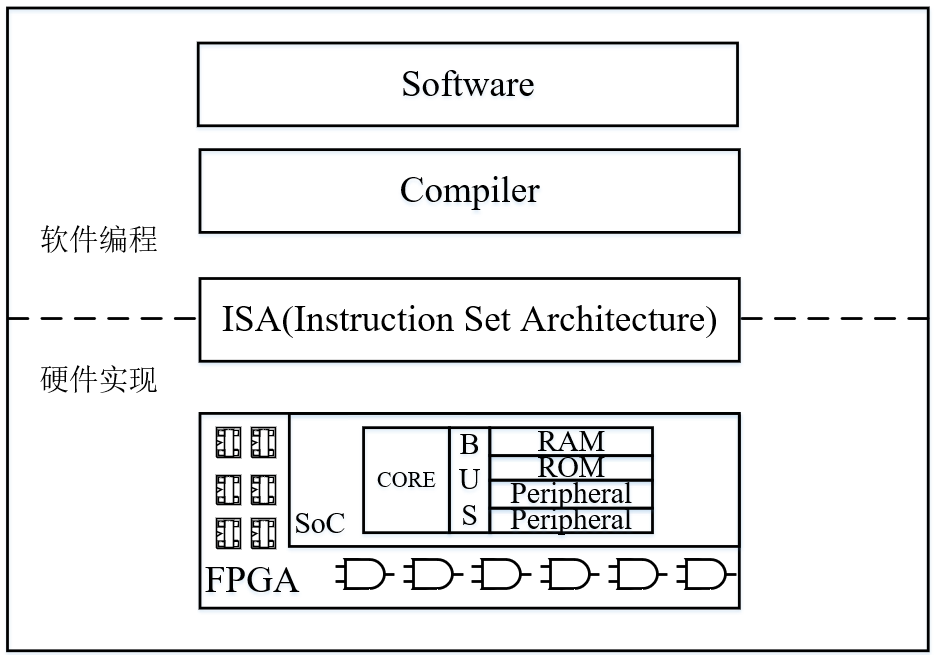

软硬件协同设计的层次结构如下图.

从下往上看(从硬件到软件), FPGA 被配置成为 SoC, SoC 的工作依赖于一条条的指令, 而指令则是由对应的汇编代码生成, 汇编代码通常又是由编译器编译高层次编程语言得到, 所以软件编程部分主要考虑的问题便是如何编写程序才可以编译出能高效地控制硬件的指令.

从上往下看(从软件到硬件), 如果想要运行编写好的软件, 首先需要利用编译器将代码编译为汇编代码, 然后将汇编代码与指令集对应生成机器码, 接着将机器码存入 SoC 的存储器中, 这时候 SoC 就能开始执行一条条的指令, 而最底层的 SoC 则需要利用 FPGA 实现.

在后续介绍的 SoC 搭建过程中, 相信大家会对软硬件协同设计的思想有更深的理解, 对软硬件协同开发的流程更加熟悉.